Received 13 December 2024; revised 27 January 2025; accepted 28 January 2025. Date of publication 31 January 2025; date of current version 21 March 2025. The review of this article was arranged by Editor A. S. Verhulst.

Digital Object Identifier 10.1109/JEDS.2025.3537290

# Electrical and 850 nm Optical Characterization of Back-Gate Controlled 22 nm FDSOI PIN-Diodes Without Front-Gate

JELLE H. T. BAKKER<sup>® 1,2</sup> (Graduate Student Member, IEEE), MARCIN Ł. MOTYCKI<sup>® 1,2</sup> (Graduate Student Member, IEEE), RAYMOND J. E. HUETING<sup>® 2</sup> (Senior Member, IEEE), ANNE-JOHAN ANNEMA<sup>® 1,2</sup> (Member, IEEE), AND MARK S. OUDE ALINK<sup>® 1,2</sup> (Senior Member, IEEE)

1 Group of Integrated Circuit Design, University of Twente, 7522 NB Enschede, The Netherlands 2 Faculty of Electrical Engineering, Mathematics and Computer Science, University of Twente, 7522 NB Enschede, The Netherlands

CORRESPONDING AUTHORS: J. H. T. BAKKER AND M. Ł. MOTYCKI (e-mail: j.h.t.bakker@utwente.nl; m.l.motycki@utwente.nl)

The work of Jelle H. T. Bakker was supported in part by the Bruco Integrated Circuits and Holland High Tech in a Public–Private-cooperation for research and development in the Hightech Systems and Materials Topsector. The work of Marcin Ł. Motycki was supported by the European Union through the Horizon Europe Project Qu-PIC under Grant 101135845. This paper was presented in part at the 50<sup>th</sup> IEEE European Solid-State Electronics Research Conference (ESSERC), September 2024.

DOI: https://doi.org/10.1109/ESSERC62670.2024.10719482.

(Jelle H. T. Bakker and Marcin Ł. Motycki contributed equally to this work.)

**ABSTRACT** We present electrical and optical ( $\lambda = 850$  nm) measurement results of back-gate controlled SOI PIN-diodes without a front-gate, with an intrinsic Si film thickness of only ~6nm. These ultrathin-body PIN-diodes were fabricated as exploratory devices in a commercially available Fully-Depleted Silicon-On-Insulator (FDSOI) technology, without requiring additional process steps. We show that electrostatic back-gate tuning significantly affects the electrical characteristics and optical responsivity ( $R_0$ ). This leads to a novel method to extract the optimal back-gate bias for maximum  $R_0$  from electrical measurements. The maximal measured  $R_0$  at 0V bias across the diode and with optimal back-gate bias equals  $62\mu$ A/W, with a -3dB bandwidth of 5.9GHz, and a -6dB bandwidth of 15GHz. These PIN-diodes potentially open the way to new (THz) circuits, sensors, novel/complementary process control monitoring structures, and optical applications. They also enable interaction between the hybrid (bulk) and SOI devices, which is a unique feature of FDSOI technologies.

**INDEX TERMS** 22 nm FDSOI, 22FDX<sup>®</sup>, PIN-diode, SOI PIN-diode, photodiode, SOI PIN PD, 850 nm, back-gate control.

# I. INTRODUCTION

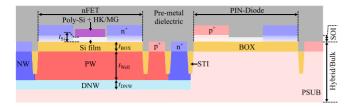

Globalfoundries<sup>®</sup> Fully-Depleted Silicon-On-Insulator (FDSOI) technology includes an extensive array of possible devices on both hybrid (bulk CMOS) and SOI within the same technology [1] (1). The 22FDX<sup>®</sup> devices built on top of the buried oxide (BOX) offer great electrostatic control and minimum gate-induced drain leakage [1]. The active intrinsic silicon (Si) film is traditionally covered by a poly-Si High-K Metal Gate (HKMG) stack, acting as a front-gate. This front-gate is the main control terminal for field-effect devices, but for some applications, for example when the Si film would be used as the intrinsic (I)-part in an SOI

PIN-diode, it can limit the electrical (*e.g.*, via additional parasitic capacitance) and optical (*e.g.*, by blocking light at the top surface) potential of the intrinsic Si film.

In this work, we present FDSOI PIN-diodes (1) without a front-gate. The presented devices have been fabricated as exploratory devices using engineering wafers in  $22FDX^{\textcircled{R}}$ , *i.e.*, without any additional process steps. This means that these devices could potentially be fabricated in any technology that uses a similar process flow. In the remainder of this work, we use the name SOI-diode instead of FDSOIdiode to prevent any potential confusion with diodes made on hybrid (bulk) area in the FDSOI-technology platform.

FIGURE 1. Cross-section of an SOI transistor, hybrid (bulk) pn-junctions, hybrid wells, and the novel SOI PIN-diode without a front-gate in 22nm FDSOI.

PIN-diodes are extremely versatile devices. For example, their fast reverse recovery phenomenon is a key element in THz pulse generators [2], frequency multipliers [3], and frequency dividers [4]. PIN-diodes are also used in voltage limiters [5], linear attenuators [6], [7], RF switches [8], and high-voltage applications [9]. Combining the reduced parasitic capacitance of the presented PIN-diodes with modern FDSOI transistors delivering superior RF performance and digital processing capabilities could result in very cost-effective and high-performance solutions. In this first iteration, however, we limit ourselves to the optical and DC electrical characteristics.

The 850nm wavelength is commonly used for optical communication, and the Si photodiode (PD) is a suitable photodetector at this wavelength [10]. Since the performance of the SOI PIN-diode depends on parameters like the SOI thickness ( $t_{Si}$ ), interface quality, and doping, these structures can also be used for Process Control Monitoring (PCM). The absence of the HKMG is essential if these devices are used as PDs for optical process monitoring, which requires top-side wafer probing for high-volume manufacturing where low monetary and time costs are crucial. For more general optical applications, back-side illumination might be an option, but then the dies have to be backgrinded and the light will still (partially) be absorbed by the Si substrate making this an undesirable option.

In traditional vertical bulk Si PDs shorter wavelengths (300 - 400 nm) are absorbed by the silicon above the depletion region, making them unable to function as photodetectors. However, there is no Si above the intrinsic Si film of the SOI PIN-diode. This makes it possible for them to perform as photodetectors for these shorter wavelengths [11]. Note that the ~6nm thick Si film [12] of the PIN-diodes will limit the responsivity ( $R_0$ ).

Combining bulk devices right below the SOI devices, as reported for Single Photon Avalanche Diodes (SPADs) [13] and back-gates (bulk wells plus BOX) [1], allows for the exploration of interactions between these bulk devices and PIN-diodes as demonstrated in this work. Back-gates in SOI technology have already been extensively used, for example, for tuning SOI FET's electrical performance [1], which is different from, *e.g.*, RF-SOI or PD-SOI where the BOX-layer as well as the SOI-layer are much thicker. The back-gate can be used to tune the charge carrier concentrations of the intrinsic Si film [14], [15], [16], [17] of the SOI PIN-diode. This is useful for improving and/or controlling electrical and optical properties like dark current and  $R_0$  [18].

Extending earlier work [19], we present additional extensive measurement results of SOI PIN-diodes without a front-gate in a commercial FDSOI process. Furthermore, we show and discuss the effect of electrostatic back-gate tuning on the charge carriers in the SOI PIN-diode that both affect the electrical characteristics and  $R_0$ . We introduce a novel method to obtain the back-gate bias for maximum  $R_0$  from purely electrical measurements. This can be leveraged to increase the  $R_0$  by an order of magnitude by setting an optimum back-gate bias voltage. This control of the  $R_0$  can also be used to compensate for, *e.g.*, process or temperature variations.

This paper is organised as follows: Section II explains the effect of the back-gate, Section III discusses the designed diode layouts, Section IV describes the experimental setups, Section V presents and discusses the electrical and optical measurement results, and in Section VI the main findings and conclusions are summarized.

#### **II. ELECTROSTATIC BACK-GATE CONTROL**

Conventional thin-film gated diodes have a current-voltage (I-V) dependency on both the front-gate and back-gate potential  $(V_{BG})$  relative to the anode  $(V_P)$  and cathode  $(V_N)$  potential [14]. Our thin-film devices do not have a front-gate, see 2, leaving only the  $V_{BG}$  (PSUB) potential to affect the *I*-*V* characteristics. Throughout this work it is assumed that  $V_{BG}$ ,  $V_N$  (n<sup>+</sup>), and  $V_P$  (p<sup>+</sup>) are defined as relative to a common ground.

Fig. 2 illustrates simplified cross-sections and energy band diagrams of the SOI PIN-diodes for various  $V_{BG}$  assuming no incident light. With the terminals  $p^+$  and  $n^+$  set to  $V_P = V_N = 0V$ , three scenarios are shown for different  $V_{BG}$ relative to  $V_{BG,max,R}$ . Here  $V_{BG,max,R}$  is defined as the  $V_{BG}$ for which the PIN-diodes have a maximum  $R_0$  when  $V_P =$  $V_N = 0V$  (as explained later in this section). At that  $V_{BG}$  the device behaves as an actual PIN-diode and, consequently, operates best as a PD for the given diode voltage.

Fig. 2(a) shows the charge carrier distribution and energy band diagram for  $V_{BG} = V_{BG,max,R}$ . In this case, there are hardly any charge carriers in the intrinsic region. For this  $V_{BG}$  the  $R_0$  will be maximum because the Si film has its maximum intrinsic Si volume. When an incident photon with  $\lambda < 1100$ nm [20] is absorbed in the Si film, an electron-hole pair is generated. Due to the electric field stemming from the built-in (lateral) potential, the generated charge carriers are quickly separated and drift towards the  $p^+$  and  $n^+$  regions, resulting in a photocurrent. For low forward voltages ( $V_{\rm PN} < 0.6 V$ ), in the absence of light, the recombination current is the dominant current component. The Shockley-Read-Hall (SRH) recombination is highest in the regions where p is equal to n and the pn product is maximal [21]. For PIN-diodes this is the case in the intrinsic region; therefore, a maximum intrinsic Si volume results in a maximum recombination current. Consequently, for a

**FIGURE 2.** Schematic illustration of the electrostatic back-gate control in SOI PIN-diodes under dark condition. (left) Charge carrier distributions in the device, and (right) horizontal energy band diagrams for different *V*<sub>BG</sub>.

given applied  $V_{PN}$  both the  $R_o$  and recombination current are maximum when  $V_{BG} = V_{BG,max,R}$ .

Differences in doping levels of the n<sup>+</sup> and p<sup>+</sup> regions as well as in the work functions of the SOI layer and the back-gate result in a  $V_{BG,max,R}$  that is not exactly 0V. The finite Debye lengths cause long tails in the lateral direction in the energy bands from the level in n<sup>+</sup> and p<sup>+</sup> to the level in the intrinsic Si. The result is that the actual fully depleted part of the intrinsic region,  $L_{C,eff}$ , is smaller than  $L_C$ , as also shown in the figure.

Fig. 2(b) shows the charge carrier distribution and energy band diagram for  $V_{BG} \ll V_{BG,max,R}$ . In this scenario, the applied  $V_{BG}$  induces a negative charge under the BOX, which attracts holes in the Si film. Since the film is ultrathin, it can be assumed that (almost) all of its volume is now full of holes [22]. The large density of attracted holes effectively increases the (p-type) doping in the Si film, turning the PIN-diode into a PPN-diode with a relatively small depletion region  $(L_D)$ . The electron-hole pairs generated outside of the narrow depletion region must now rely on slow diffusion instead of drift to be separated. This combined with the reduction of  $L_D$  and any (potential) defects in the top interface of the Si film effectively reduces  $R_0$ . Moreover, for high negative  $V_{BG}$  the ultrahigh hole concentration near the n<sup>+</sup> region could form a tunnel junction [15], which would lead to an increase of (tunnel) current.

Fig. 2(c) shows the charge carrier distribution and energy band diagram for  $V_{BG} \gg V_{BG,max,R}$ . This results in exactly the opposite to what is depicted in Fig. 2(b) resulting in a PNN-diode, thus the  $R_0$  is also expected to be significantly

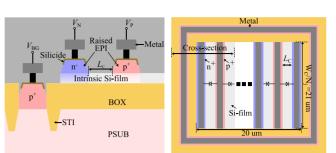

**FIGURE 3.** Schematic layout of the SOI PIN-diode without a front-gate: (left) cross-section, and (right) top view. Here  $N_j$  is the number of parallel PIN-junctions.

reduced. Similarly, an ultrahigh electron concentration could also form a tunnel junction, but then near the  $p^+$  region.

We use the principle of the electrostatic back-gate control described above in our measurements, as discussed in Section V, to characterize the device and to obtain maximum  $R_0$ .

# **III. SOI PIN-DIODE LAYOUT**

A schematic layout of the SOI PIN-diodes is shown in Fig. 3. Each device consists of several parallel-connected PIN-junctions, for characterisation sensitivity purposes. Devices were designed and fabricated with five different lengths of the intrinsic region ( $L_C$ ): 157nm, 260nm, 527nm, 1090nm, and 2127nm. The total widths ( $W_C$ ) of the parallel PIN-junctions are: 93.1  $\cdot$  10<sup>-3</sup> cm, 71.9  $\cdot$  10<sup>-3</sup> cm, 50.8  $\cdot$  10<sup>-3</sup> cm, 29.6  $\cdot$  10<sup>-3</sup> cm, and 16.9  $\cdot$  10<sup>-3</sup> cm, respectively. These widths are used to report dimension-independent currents per unit width (A/cm). The area (including metal wiring) for all devices is 21 $\mu$ m × 20 $\mu$ m, which aligns with the typical beam sizes of fibre-coupled lasers. Metal coverage of the diodes (in the Back End Of Line (BEOL)) was minimised to reduce light blockage. The metal area has been subtracted from the device area when calculating  $R_0$ .

# **IV. EXPERIMENTAL SETUP**

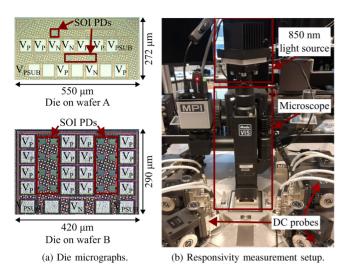

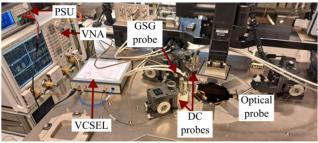

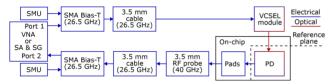

We studied devices from two 22FDX® wafers (A and B). Fig. 4(a) shows single dies containing test structures on wafers A and B respectively. Wafer A allows for RF measurements with a Ground-Signal-Ground (GSG) probe (FormFactor Infinity I40). Wafer B contains more device variants but only allows for DC measurements. All measurements were done on a probe station (MPI TS300-SE). I-V sweeps were measured with a semiconductor parameter analyser (Keithley 4200). Ro (A/W) (is explained in detail in Section V.D) measurements were done with a custom calibrated 850nm light source consisting of IR-LEDs (OSLON<sup>®</sup> 9 IR PowerClusters) followed by an optical 10nm filter (Thorlabs FBH850-10) (Fig. 4(b)). The frequency response measurements use a Vertical Cavity Surface Emitting Laser (VCSEL) (VI Systems V50-850M). The VCSEL's calibration data consists of  $S_{11}$  (measured

(c) S-parameter measurement setup.

(d) Schematic block diagram of the frequency response measurement setups.

at the electrical input of the VCSEL) and  $|S_{21}|$  (from the electrical input to the optical output power of the VCSEL. For the Device Under Test (DUT), the  $|S_{21}|$  is from the optical input (port 1) to the electrical output (port 2) [23]. The VCSEL output is connected to a lensed fibre (Thorlabs LFM1F-1) that is aligned using a micromanipulator above the DUT.

The frequency (*f*) response was measured with two measurement setups (Fig. 4(d)). For measurements at f > 0.5GHz, a Vector Network Analyser (VNA) (Keysight N5244A) was used (Fig. 4(b)) (port 1 of the VNA was calibrated up to the connector of the VCSEL). Port 2 of the VNA is connected to the GSG RF probe, which was calibrated using an Impedance Standard Substrate (ISS) (Cascade 101-190), and is connected to the on-chip pads. The signal needle of the GSG RF probe connects to the cathode ( $V_{\rm N}$ ) and both ground needles connect to the anode ( $V_{\rm P}$ ). The capacitance between the on-chip signal (pad and trace) and ground (pads and traces) was measured and deembedded on a separate (open) de-embed structure.

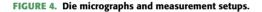

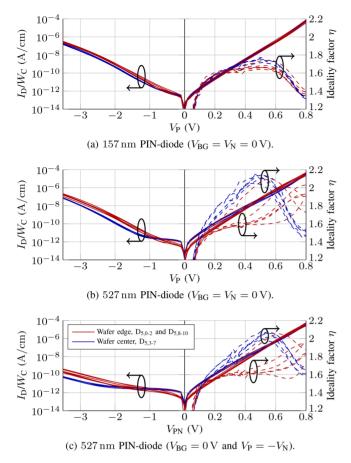

**FIGURE 5.** Gummel plot (drawn curves) and calculated ideality factor (dashed curves) as a function of  $V_{PN}$  of five PIN-diodes on the same reticle (D<sub>4,3</sub>) on wafer B with  $V_{BG} = V_{BG,max,R}$  and  $V_P = -V_N$ .

The low  $R_0$  of the DUT resulted in a too low output signal that could not accurately be measured by the VNA for  $f \le 0.5$ GHz. Therefore, for  $f \le 0.5$ GHz, a Signal Generator (SG) (Agilent E8267D-544) and a Signal Analyser (SA) (Agilent N9030A) with a lower noise floor were used. The used GSG RF probe and cables were first characterized with a VNA and de-embedded from the measurements along with the VCSEL. The on-chip capacitance was not de-embedded for these low frequencies.

# V. RESULTS AND DISCUSSION

# A. I-V RETICLE MEASUREMENTS

The measured *I-V* characteristics (or Gummel plots) of five PIN-diodes with varying  $L_{\rm C}$  located on one reticle are shown in Fig. 5. Here  $V_{\rm BG} = V_{\rm BG,max,R}$  (obtained from optical measurements as discussed further in this section). Based on the exponential relation between  $I_{\rm D}$  and  $V_{\rm PN}$  ( $V_{\rm PN} > 0V$ ) it can be concluded that the diodes are electrically functional.

The forward characteristics, *i.e.*, for  $V_{\rm PN} > 0$ , indicate an increased series resistance for larger  $L_{\rm C}$ , suggesting that a longer resistive intrinsic region limits the maximum current.

$L_{\rm C}$  also influences the slopes of the forward characteristics, expressed in ideality factor ( $\eta$ ), which is calculated from (a fit of) the measured current ( $I_{\rm D}$ ) using the Shockley equation [20]:

$$I_{\rm D} = I_{\rm sat} \left( e^{\frac{V_{\rm PN}}{\eta V_{\rm T}}} - 1 \right) \tag{1}$$

where  $I_{\text{sat}}$  is the saturation current,  $V_{\text{T}} = kT/q$  is the thermal voltage (equal to 25.9mV at room temperature), k is Boltzmann's constant, T is the temperature, and q is the elementary charge.

According to theory, for the  $V_{\text{PN}}$  range in which the SRH recombination current is dominant,  $\eta$  should be equal to 2 [20]. This, together with  $I_{\text{sat}}$ , is related to the SRH recombination rate which can be expressed as [20], [21]:

$$R_{\rm SRH} \approx \frac{pn}{\tau_{\rm SRH}(n+p+2n_i)},$$

(2)

where *p* is the hole concentration, *n* is the electron concentration,  $n_i$  is the intrinsic carrier concentration and  $\tau_{\text{SRH}}$  is the (effective) SRH recombination lifetime (assuming the hole lifetime equals the electron lifetime). The SRH

recombination is most efficient in the regions where p is equal to n and the pn product is maximal [21]. For PIN-diodes this is the case in the intrinsic region.

From the measured forward characteristics it was found that  $\eta$  is not equal to 2 for the  $V_{\rm PN}$  regime where the recombination current is expected to dominate. Instead, a steady increase of  $\eta$  as a function of  $V_{\rm PN}$  for  $V_{\rm PN} > 0.2V$ can be seen, followed by an abrupt decrease. Its maximum value increases with increasing  $L_{\rm C}$  and tends to occur at  $V_{\rm PN} \approx 0.6V$ . This dependency of  $\eta$  on both  $V_{\rm PN}$  and  $L_{\rm C}$  can be explained by the fact that  $L_{\rm C}$  is reduced by finite Debye lengths as mentioned in Section II. The resultant reduction of the intrinsic volume lowers the recombination current. Below a certain  $L_{\rm C}$ , this effect causes the PIN-diode to act like a PN-diode.

For longer devices, as  $V_{\rm PN}$  is increased, the quasi-Fermi levels split more, and the potential barrier between  $V_{\rm P}$  and  $V_{\rm N}$ lowers, thus more charge is injected into the intrinsic region. The lengths of the transition tails between the intrinsic region and n<sup>+</sup> as well as p<sup>+</sup> also reduce, increasing  $L_{\rm C,eff}$  which translates to the increase of the intrinsic volume. This causes the saturation current of the diode ( $I_{\rm sat}$ ) to be  $V_{\rm PN}$ -dependent and is visible in the Gummel plots as an increase of  $\eta$ . At a certain point the resultant  $L_{\rm C,eff} \approx L_{\rm C}$ . In this situation, the  $I_{\rm sat}$  of the recombination current saturates at its maximum value. Then  $\eta$  reaches its peak value and ideally settles at 2.

For  $V_{\rm PN} > 0.6$ V, diffusion starts to dominate due to the injection of minority carriers into p<sup>+</sup> and n<sup>+</sup>, which is exponentially dependent on  $V_{\rm PN}$ . Since  $\eta$  should be unity when diffusion currents dominate, a sudden drop in  $\eta$  can be observed for  $L_{\rm C} \leq 1090$ nm for that  $V_{\rm PN}$  range.

At relatively high current densities, series resistance reduces the slope of  $I_D$ , which translates to an increase in  $\eta$ . As can be observed in the figure, the series resistance for maximum  $L_C$  (2127nm) is so large that it precedes the onset of the diffusion current so that  $\eta$  does not first bend towards unity after reaching 2. Instead, it keeps increasing. The abnormally large  $\eta$  values visible in Fig. 5 and the probable cause is elaborated on in Section V.C.

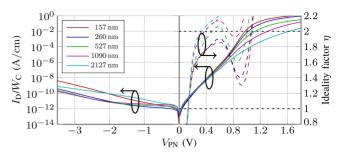

Fig. 6 shows the maximum recombination current per unit width  $(I_{\text{sat,max}}/W_{\text{C}})$  as a function of  $L_{\text{C}}$ . Here  $V_{\text{BG}}$  is set to  $V_{\text{BG,max,rec}}$ , which is defined as the  $V_{\text{BG}}$  for which there is maximum recombination current ( $\eta$  is close to 2) for a given  $V_{\text{P}}$  and  $V_{\text{N}}$ .  $V_{\text{BG,max,rec}}$  should not be confused with  $V_{\text{BG,max,R}}$ . The saturation current was calculated using Eq. (1) with the measured  $I_{\text{D}}$  and the assumption that  $\eta = 2$ .

In the figure, the measurements for four different reticles are presented. The standard deviation is shown with error bars. The average  $I_{\text{sat,max}}/W_{\text{C}}$  seems to increase linearly with  $L_{\text{C}}$  up to 527nm. An increase in  $L_{\text{C}}$  translates to a linear increase of the volume where recombination takes place (*i.e.*, intrinsic region) assuming a fixed charge carrier density. Thus there is a linear relation between  $I_{\text{sat}}$  and  $L_{\text{C}}$ , until  $L_{\text{C}}$  approaches or exceeds the diffusion length:

FIGURE 6.  $I_{sat,max}/W_C$  against  $L_C$  on wafer B for  $V_{PN} = 0.2V$ ,  $V_{BG} = V_{BC,max,rec}$  and  $V_P = -V_N$ .

then significantly more carriers recombine before they reach the p<sup>+</sup> or n<sup>+</sup> regions. This results in a deviation from the linear dependence, as seen for devices longer than 527nm. First  $I_{\text{sat,max}}/W_{\text{C}}$  starts to saturate for the 1090nm devices, and finally decreases for the 2127nm devices. Note that the diffusion length depends on both the interface quality and SOI quality. It is expected that the diffusion lengths of 22FDX<sup>®</sup> will be in the same order of magnitude as the diffusion lengths of the 28nm FDSOI process reported by Lee et al. [24], where a minority carrier lifetime ( $\tau_{eff}$ ) of 5-10ns was found, suggesting a hole diffusion length of ~300nm. Thus in the case of the 2127nm device, the *pn* product has reduced in a large portion of the intrinsic region.

# **B. I-V WAFER MEASUREMENTS**

Fig. 7 shows the measured *I-V* characteristics (Gummel plots) with ideality factors of PIN-diodes across an entire row on wafer A. In Fig. 7(a) and 7(b)  $V_{BG} = V_N = 0V$  and anode potential  $V_P$  is swept. PIN-diodes on reticles closer to the edge of the wafer, D<sub>5,0-2</sub> and D<sub>5,8-10</sub> (Fig. 8), have higher currents when reverse biased. This is especially visible for the devices with  $L_C$  equal to 527nm.

Based on conventional bulk diode behaviour, the reverse bias current is expected to be more or less constant before going into avalanche [20]. However, Fig. 7 shows a significant increase in current for stronger reverse bias. This is likely caused by additional conduction paths or trapassisted tunnelling as indicated by the different back-gate potential dependencies in Fig. 7(b) and 7(c). As discussed in Section II, tunnel junctions can be formed when a high  $V_{BG}$  is applied which, combined with traps caused by local defects, results in trap-assisted tunnelling. On top of that, due to the asymmetry in the devices (doping or work function differences) tunnel junctions may have already formed for  $V_{BG} = 0V$ .

Fig. 7 shows that the 527nm devices have a higher  $\eta$  than the 157nm devices. The highest value for  $\eta$  on wafer A was found to be ~2.1 for the devices with  $L_{\rm C}$  equal to 527nm. For the 157nm devices, the lower ideality factor is most likely due to the smaller lengths of their intrinsic regions and surface areas, which lowers the recombination current. In contrast, the diffusion currents are expected to be

**FIGURE 7.** Gummel plots and calculated ideality factors of SOI PIN-diodes across wafer A for different back-gate ( $V_{BG}$ ), anode ( $V_{P}$ ), cathode ( $V_{N}$ ) biasing, and physical length of the intrinsic region  $L_{C}$ . The curves corresponding to the reticles close to the edge of the wafer ( $D_{5,0-2}$  and  $D_{5,8-10}$ ) are red and those close to the centre ( $D_{5,3-7}$ ) are blue. Note the different scale on the horizontal axis for positive and negative values.

independent of  $L_{\rm C}$  as long as  $L_{\rm C}$  is much smaller than the diffusion lengths of the electrons and holes.

Differences between Fig. 7(b) and 7(c) in the currents and ideality factors stem from different biasing approaches. The asymmetric biasing in the former plot causes a significant increase in the reverse current and relatively large  $\eta$  values (above 2). Keeping  $V_{BG} = V_N$  while sweeping  $V_P$  results in the intrinsic region effectively experiencing a changing potential difference between itself and the back-gate. As explained in Section II, the result is a dynamical change in electrostatic doping. An approach that mitigates this effect is symmetric biasing, implemented by forcing  $V_P = -V_N$  as done for Fig. 7(c). This biasing method sets an almost static potential difference between the back-gate and the centre of the intrinsic region; this is used throughout Section V.C.

The Gummel plots in Fig. 7 show that the 527nm devices near the wafer edge have lower recombination currents, lower maximum  $\eta$  values, and reverse characteristics more similar to shorter devices. This likely suggests that the devices near the wafer edge have an effectively lower  $L_{\rm C}$  than the devices in the centre.

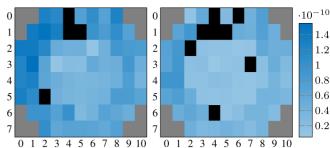

**FIGURE 8.** Wafer map showing  $I_D/W_C$  (A/cm) for the (left) 157nm and (right) 527nm devices on wafer A. Gray squares are outside of the wafer and black squares are samples that were accidentally destroyed in earlier measurements ( $V_{BG} = V_N = 0V$  and  $V_P = -1.5V$ ).

**FIGURE 9.** Diode current  $(I_D/W_C)$  against  $V_{BG}$  for varying  $V_{PN}$  (20mV steps), with  $V_P = -V_N$  across wafer B. (left)  $D_{4,3}$  with  $L_C = 527$ nm and (right)  $D_{4,3}$  with  $L_C = 2127$ nm.

Fig. 8 shows a wafer map of measured  $I_D/W_C$  of our 157nm (72 devices) and 527nm (68 devices) SOI PIN-diodes at  $V_{BG} = V_N = 0V$  and  $V_P = -1.5V$ . A clear circular pattern is observed, which stems from process-related factors, *e.g.*, the device processing or stress caused by the BEOL. In particular, the absolute current differences are less for shorter devices, indicating a dependency between  $L_C$  and location-dependent variations in the *I-V* curves. Such sensitivity to process-related aspects could be useful in PCM structures and general reliability monitoring.

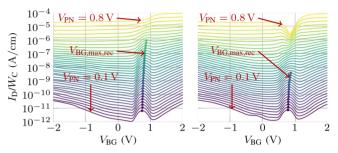

# C. I-V BACK-GATE CONTROL

Similar to earlier work [14], [17], Fig. 9 shows  $I_D/W_C$  as a function of  $V_{BG}$ , for  $V_{PN}$  between 0.1V to 0.8V. A change in  $V_{BG}$  modulates the carrier concentrations (*n* and *p*), which also changes  $R_{SRH}$  conform Eq. (2). This dependence yields maxima in the measured currents, at  $V_{BG} = V_{BG,max,rec} \approx 0.8V$ . In Fig. 9 these maxima are marked by thick dots. At  $V_{BG,max,rec}$ , the intrinsic region has maximum volume and the diode behaves like a PIN-diode as explained in Section II.

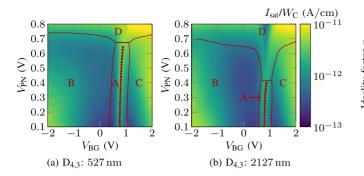

Eq. (1) and the measurements shown in Fig. 9 are used to estimate  $I_{sat}$ , which is plotted as a function of  $V_{PN}$  and  $V_{BG}$  in Fig. 10.  $I_{sat}$  was chosen instead of  $I_D$  because it does not have an exponential dependence on  $V_{PN}$ , which helps in the visualization and analysis of the back-gate effect and its influence on the operation of the device. In these contour plots, four different regions can be identified. Region A corresponds to the PIN-diode operating region (conform

**FIGURE 10.** Contour plots of  $I_{sat}/W_{C}$  of the PIN-diode when sweeping  $V_{BG}$  and  $V_{PN}$  ( $V_{P} = -V_{N}$ ), used to estimate  $V_{BG,max,R}$ .

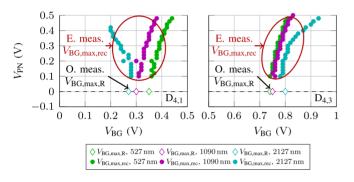

**FIGURE 11.**  $V_{BG,max,rec}$  from electrical (E.) measurements (circles) compared to  $V_{BG,max,R}$  from optical (O.) measurements (diamonds), (left)  $D_{4,1}$  and (right)  $D_{4,3}$  on wafer B.

Fig. 2(a)) where the recombination current is dominating and (close to) maximal, indicating intrinsic Si. The red markers are the  $V_{BG,max,rec}$  for varying  $V_{PN}$ . Regions B and C correspond to the  $V_{BG}$  and  $V_{PN}$  range where the intrinsic region is electrostatically doped such that the diode behaves as a PN-diode (conform respectively Fig. 2(b) and 2(c)). Here the asymmetry between regions B and C is likely caused by differences in the epitaxially grown n<sup>+</sup>/p<sup>+</sup> doped Si. Region D is where diffusion currents and/or series resistance dominate over the recombination current, obfuscating  $V_{BG,max,rec}$ .

Fig. 11 shows  $V_{BG,max,rec}$  against  $V_{PN}$  as taken from the electrical measurements, and  $V_{BG,max,R}$  acquired from the optical measurements for  $V_{PN} = 0V$ . It is shown that points located at  $(V_{BG,max,rec}, V_{PN})$  converge to  $(V_{BG,max,R}, 0V)$ . This occurs because as  $V_{PN}$  approaches 0V, the difference between  $V_{BG,max,R}$  and  $V_{BG,max,rec}$  is expected to decrease as both  $R_o$  and  $R_{SRH}$  are maximal when a PIN-diode with the largest possible intrinsic Si volume is electrostatically formed. Here results obtained from two different reticles are shown to illustrate how  $V_{BG,max,rec} \approx V_{BG,max,R}$  for  $V_{PN} \leq 0.2V$ .

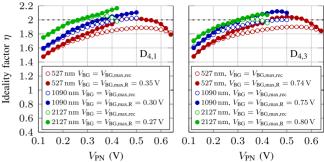

Fig. 12 shows the difference between  $\eta$  for  $V_{BG} = V_{BG,max,rec}$  and  $V_{BG} = V_{BG,max,R}$ , where  $V_{BG,max,rec}$  is  $V_{PN}$  dependent and  $V_{BG,max,R}$  is determined at  $V_{PN} = 0V$ . The devices do indeed behave more like PIN-diodes ( $\eta =$

FIGURE 12. Calculated ideality factor ( $\eta$ ) against  $V_{PN}$  for  $V_{BG} = V_{BG,max,rec}$  and  $V_{BG} = V_{BG,max,R}$ , with  $V_P = -V_N$ , (left)  $D_{4,1}$ , and (right)  $D_{4,3}$  on wafer B.

2) when they are optimally biased ( $V_{BG} = V_{BG,max,rec}$ ).  $V_{BG} = V_{BG,max,rec}$  can, for example, be supplied with a suitable (tracking) biasing circuit when a PIN-diode behaviour is required. This circuit would need to apply the average signal across the PIN-diode to the back-gate. The design of such a biasing circuit is beyond the scope of this paper.

The differences between the estimated  $V_{BG,max,R}$  and the  $V_{BG,max,rec}$  as acquired from optical measurements are shown in Fig. 13, and discussed in V.D.

# D. RESPONSIVITY MEASUREMENTS

The  $R_0$  is defined as the ratio of photocurrent and optical input power [25], [26]:

$$R_{\rm o} = \frac{I_{\rm PD}}{P_{\rm O}} = \frac{q}{E_{\rm p}} \eta_{\rm EQE, PD},\tag{3}$$

where  $I_{PD}$  is the photocurrent,  $P_O$  is the optical input power,  $E_p$  is the photon energy, and  $\eta_{EQE,PD}$  is the external quantum efficiency.  $\eta_{\rm EOE,PD} (\propto \eta_{\rm F} \eta_{\rm A})$  is the product of several ratios [26]:  $\eta_{\rm F}$  (~0.72 [26]) is the fraction of  $P_{\rm O}$  that is not reflected by the BEOL, and  $\eta_{\rm A}$  is the fraction of optical power absorbed inside the PD. Using  $\eta_{\rm A} = 1 - e^{-\alpha_{\rm 0a} \cdot t_{\rm Si}}$ , with  $\alpha_{\rm 0a}$  the absorption coefficient of Si at 850nm ( $\alpha_{oa} \approx 0.04/\mu m$ ) [10] and  $t_{Si}$  is ~6nm [12],  $\eta_A = 2.4 \cdot 10^{-4}$ . The ultra-thin SOI layer thickness in this technology limits the total percentage of absorbed light ( $\sim 0.02\%$  at 850nm when illuminated from above), which is significantly less in comparison to regular bulk devices [26]. Quantum confinement for  $\sim 6$ nm  $t_{Si}$  will become significant (resulting in a different  $\eta_A$  and thus  $R_0$ ), and trap-assisted recombination would result in a lower  $R_0$ , but to a first approximation these effects are neglected. Using these results  $\eta_{\rm EOE PD}$  is calculated to be  $1.5 \cdot 10^{-4}$  and thus  $R_0$  is expected to be in the order of  $100\mu$ A/W.

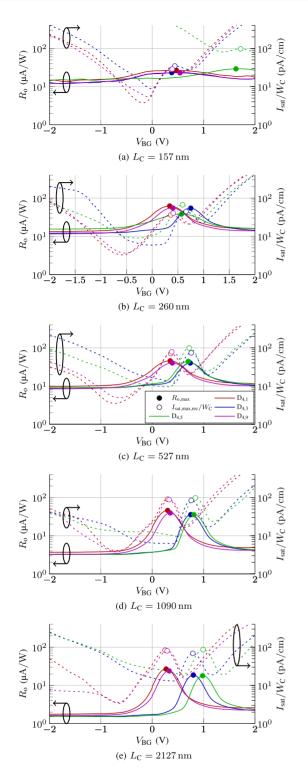

Fig. 13 shows  $R_{\rm o}$  versus  $V_{\rm BG}$  of the PDs for devices with different  $L_{\rm C}$  situated on four reticles on wafer B, with  $V_{\rm PN} = 0$ V and a uniform illumination ( $\sim 125 nW/\mu m^2$ ).  $R_{\rm o}$ is maximal ( $62\mu$ A/W, in line with the simple first-order  $R_{\rm o}$ calculation) at  $V_{\rm BG,max,R}$ , where the device has the optimal electric field distribution (fastest electron-hole separation)

FIGURE 13. Responsivity measurements (solid curves) and  $I_{sat}/W_C$  (dashed curves) as a function of  $V_{BG}$  for various SOI PIN-diodes on four reticles and five different  $L_C$ . The  $R_0$  was obtained with  $V_{PN} = 0$ V and uniform light (wavelength of 850nm and power density  $\sim 125 nW/\mu m^2$ ) across wafer B.  $I_{sat}/W_C$  was obtained with  $V_{PN} = 0.2$ V. The maximum values for both  $R_0$  ( $R_{0,max}$ ) and  $I_{sat}/W_C$  ( $I_{sat,max}/W_C$ ) have been indicated with matters.

and largest intrinsic Si volume size (largest amount of electron-hole generation). This  $R_{\rm o}$ -dependence on  $V_{\rm BG}$  has also been reported in [18].

# TABLE 1. $V_{BG,max,R}$ and $V_{BG,max,rec}$ comparison and their effect on $R_0$ and $R_0/W_C$

|                  | $^{1} \Delta V_{ m BG} $          |                                  |                                                                                         | <sup>1</sup> Responsivity                                                 |                                 |                                |  |

|------------------|-----------------------------------|----------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------|--------------------------------|--|

| $L_{\rm C}$ (nm) | <sup>2</sup> Avg.<br>diff.<br>(V) | <sup>3</sup> Std.<br>dev.<br>(V) | $\begin{array}{c} {}^{4}\text{Avg.} \\ R_{\text{o,max}} \\ (\mu\text{A/W}) \end{array}$ | $^{4}$ Avg.<br>$R_{ m o,max}/W_{ m C}$<br>$(\mu { m A}/({ m cm\cdot W}))$ | <sup>5</sup> Avg.<br>diff.<br>% | <sup>3</sup> Std.<br>dev.<br>% |  |

| 157              | 0.10                              | 0.03                             | 26                                                                                      | 274                                                                       | 0.40                            | 0.34                           |  |

| 260              | 0.04                              | 0.03                             | 53                                                                                      | 730                                                                       | 2.17                            | 2.72                           |  |

| 527              | 0.02                              | 0.01                             | 42                                                                                      | 836                                                                       | 0.45                            | 0.24                           |  |

| 1090             | 0.02                              | 0.01                             | 39                                                                                      | 1322                                                                      | 0.40                            | 0.41                           |  |

| 2127             | 0.02                              | 0.01                             | 22                                                                                      | 1292                                                                      | 0.16                            | 0.19                           |  |

<sup>1</sup> The averages (avg.) and standard (std.) deviations (dev.) are calculated for the D<sub>4,1</sub>, D<sub>4,3</sub>, D<sub>4,5</sub>, D<sub>4,7</sub>, and D<sub>4,9</sub> reticles on wafer B.

$^{2}V_{BG,max,R}$  ( $V_{PN} = 0$  V) is obtained from optical and  $V_{BG,max,rec}$  ( $V_{PN} = 0.2$  V) is obtained from electrical measurements. The absolute difference (diff.) is calculated between  $V_{BG,max,R}$  and  $V_{BG,max,rec}$ .

<sup>3</sup> Standard deviation of the average difference.

<sup>4</sup> Average measured at  $V_{BG} = V_{BG,max,R}$  and  $V_{PN} = 0$  V.

<sup>5</sup> Difference between  $R_{o,max}$  and the  $R_{o}$  measured with  $V_{BG} = V_{BG,max,rec}$ and  $V_{PN} = 0 \text{ V}$ .  $V_{BG,max,rec}$  is determined at  $V_{PN} = 0.2 \text{ V}$ .

Fig. 13 also plots  $I_{\text{sat}}/W_{\text{C}}$  for  $V_{\text{PN}} = 0.2 \text{V}$  ( $V_{\text{PN}} =$ 0V would result in 0A for purely electrical measurements). Near the  $I_{\rm sat}/W_{\rm C}$  and  $R_{\rm o}$  maxima ( $V_{\rm BG} \approx V_{\rm BG,max,R} \approx$  $V_{BG,max,rec}$ ), the  $I_{sat}/W_{C}$  and  $R_{o}$  measurements have similar trends, indicating a direct correlation between the dependencies of  $I_{\rm sat}/W_{\rm C}$  and  $R_{\rm o}$  on  $V_{\rm BG}$ . For  $V_{\rm BG}$  «  $(V_{BG,max,R}, V_{BG,max,rec})$  and  $V_{BG} \gg (V_{BG,max,R}, V_{BG,max,rec})$ , an increase in  $I_{\text{sat}}/W_{\text{C}}$  can be observed, contrary to the  $R_{\rm o}$  which slowly decreases. The increase in  $I_{\rm sat}/W_{\rm C}$  is likely due to the formation of tunnel junctions for the cases where a high concentration of carriers is present in the iregion as explained in Section II. For both  $I_{sat}/W_{C}$  and  $R_{\rm o}$ , an actual PIN-diode has been electrostatically obtained at a  $V_{BG} = V_{BG,max,R} \approx V_{BG,max,rec}$ , which results in maximal SRH recombination current (at  $V_{PN} > 0V$ ) and maximal photogeneration current (at  $V_{\rm PN} = 0$ V).

Table 1 compares the optically measured  $V_{BG,max,R}$  to the electrically measured  $V_{BG,max,rec}$  ( $V_{PN} = 0.2V$ ) for the  $L_C = 157$ nm, 260nm, 527nm, 1090nm, and 2127nm devices. The absolute difference between  $V_{BG,max,R}$  and  $V_{BG,max,rec}$  is between 10mV and 100mV (note that the used  $V_{BG}$  sweep step size during measurements is 10mV), thus proving that  $V_{BG,max,rec}$  ( $V_{PN} = 0.2V$ ) is a reasonable estimate for  $V_{BG,max,R}$ . This bias voltage also results in  $R_o \approx R_{o,max}$ . The maximum average  $R_{o,max}$  was measured for the 260nm device (53 $\mu$ A/W). For the  $R_o$  normalized to  $W_C$ , the largest value was measured for the 1090nm device (1322 $\mu$ A/(cm·W)).

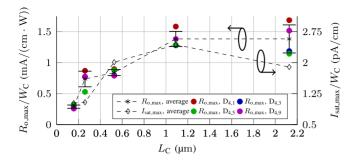

In Fig. 14 the  $R_{o,max}/W_C$  is plotted against  $L_C$  for various devices across wafer B. This curve shows an almost identical behaviour to the  $I_{sat}/W_C$  versus  $L_C$  curve also plotted in Fig. 6. It first increases linearly up to 1090nm because  $R_o/W_C$  is linearly dependent on  $L_C$ . Above 1090nm the  $R_o$  stops increasing, most probably due to a combination of phenomena related to the increased  $L_C$ , such as, *e.g.*, the reduction of the electric field across the diode and the  $L_C$

**FIGURE 14.**  $R_{o,max}/W_C$  with  $V_{BG} = V_{BG,max,R}$  and  $V_N = V_P = 0V$  against  $L_C$  across wafer B.  $I_{sat,max}/W_C$  with  $V_{BG} = V_{BG,max,rec}$ ,  $V_{PN} = 0.2V$ , and  $V_N = -V_P$  against  $L_C$  across wafer B.

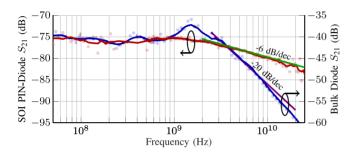

**FIGURE 15.** Frequency response of (left y-axis) the SOI PIN-diode with  $L_{C} = 527nm$  (wafer A) and  $V_{BG} = V_{P} = V_{N} = 0V$ , and (right y-axis) a bulk (hybrid) PW/NW PD from [26] fabricated in the same technology with a diode bias voltage of 0V. The bulk diode is located on a separate die from a different wafer lot.

surpassing the diffusion lengths of the carriers inside the intrinsic region.

The SOI layer is located between two materials with a low dielectric constant, effectively forming a waveguide. Coupling light into this waveguide would be challenging due to the thickness of the BOX (20nm [12]) and Si film (~6nm [12]), but if done properly, it would result in the light being absorbed along the lateral dimension of the back-gate controlled SOI PIN-diode with the possibility of improving  $R_0$  by orders of magnitude without losing any of the other benefits. That would open up (many) more optical applications for these PIN-diodes.

#### E. FREQUENCY RESPONSE

Fig. 15 shows the measured optical to electrical frequency response of both the SOI PIN-diode (wafer A) and a hybrid (bulk) NW/PW PD fabricated in the same technology [26].

The SOI PIN PD  $R_o$  is  $62\mu$ A/W and the BW<sub>-3dB</sub> and BW<sub>-6dB</sub> are 5.9GHz and 15GHz, respectively. For comparison, the bulk NW/PW PD in the same technology for the same bias conditions has a  $R_o$  of 6mA/W and a BW<sub>-3dB</sub> and BW<sub>-6dB</sub> of 3.9GHz and 5.4GHz respectively [26]. Fig. 15 shows that the roll-off of the SOI PIN-diode is (much) less steep than for its hybrid counterpart. This better frequency response is likely due to the lower junction capacitance and larger depleted/intrinsic Si volume relative to the non-depleted/doped Si volume (where light can also be absorbed) of the SOI PIN PD compared to the bulk PD. This alleviates equalisation requirements and could be beneficial for (very) high bandwidth applications.

#### **VI. CONCLUSION**

Experimental back-gate controlled SOI PIN-diodes without a front-gate were fabricated as exploratory devices in a commercially available FDSOI technology, without requiring additional process steps. This means that these devices can be fabricated in any technology that uses a similar process. They are found to be functional, both electrically and optically. The measured responsivities at a wavelength of 850nm are  $2 - 62\mu A/W$ . The obtained BW<sub>-3dB</sub> and BW<sub>-6dB</sub> are 5.9GHz and 15GHz, respectively.

Electrostatic back-gate tuning shows a significant effect on the electrical characteristics and responsivity as predicted by theory. A method to estimate the optimal back-gate voltage for maximum responsivity solely based on electrical measurements has been proposed and demonstrated to be functional.

The presented SOI PIN-diodes open the way to new THz circuits, PCM structures, and optical applications, and enable new interfacing possibilities between the hybrid (bulk) and SOI layers via electrostatic interaction.

#### ACKNOWLEDGMENT

The authors would like to thank GlobalFoundries for providing silicon fabrication through the 22FDX university program. They also want to thank Jurriaan Schmitz and Bram Nauta (University of Twente) for the fruitful discussions and Luca Pirro and Michael Zier (GlobalFoundries) for helping with the 22FDX<sup>®</sup> technology aspects. Views and opinions expressed are however those of the authors only and do not necessarily reflect those of the European Union or the European Commission. Neither the European Union nor the European Commission can be held responsible for them.

# REFERENCES

- R. Carter et al., "22nm FDSOI technology for emerging mobile, Internet-of-Things, and RF applications," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, 2016, pp. 2.2.1–2.2.4.

- [2] S. Razavian and A. Babakhani, "A THz pulse radiator based on PIN diode reverse recovery," in *Proc. IEEE BiCMOS Compd. Semicond. Integr. Circuits Technol. Symp.*, 2019, pp. 1–4.

- [3] S. Thomas et al., "A 0.4-4 THz p-i-n diode frequency multiplier in 90-nm SiGe BiCMOS," *IEEE J. Solid-State Circuits*, vol. 58, no. 9, pp. 2407–2420, Sep. 2023.

- [4] S. Thomas, B. F. Motlagh, and A. Babakhani, "A 132-204 GHz carrier storage frequency divider with sub-50 micro-watt DC power," in *Proc. IEEE BiCMOS Compd. Semicond. Integr. Circuits Technol. Symp.*, 2024, pp. 221–224.

- [5] S. Deng, C. Gao, S. Chen, J. Sun, and K. Wu, "Research on linearity improvement of silicon-based p-i-n diode limiters," *IEEE Microw. Wireless Compon. Lett.*, vol. 30, no. 1, pp. 62–65, Jan. 2020.

- [6] B.-J. Jang, "Voltage-controlled PIN diode attenuator with a temperature-compensation circuit," *IEEE Microw. Wireless Compon. Lett.*, vol. 13, no. 1, pp. 7–9, Jan. 2003.

- [7] W. He, J. Li, K.-D. Xu, S. Yan, and J. Chen, "Voltage-controlled tunable filtering attenuator using PIN diodes," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 71, no. 2, pp. 562–566, Feb. 2024.

- [8] F. Ghorbani, A. Dayan, J. Zhou, Y. Huang, A. G. Schuchinsky, and M. Gustafsson, "Linearity enhancement in PIN-diode-based switches," *IEEE Trans. Microw. Theory Tech.*, vol. 73, no. 2, pp. 789–800, Feb. 2025.

- [9] R. H. Caverly and G. Hiller, "Establishing the minimum reverse bias for a p-i-n diode in a high-power switch," *IEEE Trans. Microw. Theory Tech.*, vol. 38, no. 12, pp. 1938–1943, Dec. 1990. [Online]. Available: http://ieeexplore.ieee.org/document/64577/

- [10] F. Tavernier and M. Steyaert, High-Speed Optical Receivers with Integrated Photodiode in Nanoscale CMOS, 1st ed. New York, NY, USA: Springer, 2011, doi: 10.1007/978-1-4419-9925-2.

- [11] F. O. S. Silva and R. T. Doria, "Suitability of applying ultrathin SOIbased PIN diodes to photodetection of UV wavelength," *Electron. Lett.*, vol. 60, no. 8, 2024, Art. no. e13177.

- [12] T. Xie, Q. Wang, H. Ge, Y. Lv, Z. Ren, and J. Chen, "Characterization of 22 nm FDSOI nMOSFETs with different backplane doping at cryogenic temperature," *IEEE J. Electron Devices Soc.*, vol. 9, pp. 1030–1035, 2021. [Online]. Available: https://ieeexplore.ieee.org/ document/9582809/

- [13] T. C. de Albuquerque et al., "Integration of SPAD in 28nm FDSOI CMOS technology," in *Proc. Eur. Solid-State Device Res. Conf.* (ESSDERC), 2018, pp. 82–85. [Online]. Available: https://ieeexplore. ieee.org/document/8486852/

- [14] T. Ernst, S. Cristoloveanu, A. Vandooren, T. Rudenko, and J.-P. Colinge, "Recombination current modeling and carrier lifetime extraction in dual-gate fully-depleted SOI devices," *IEEE Trans. Electron Devices*, vol. 46, no. 7, pp. 1503–1509, Jul. 1999.

- [15] S. Cristoloveanu, K. H. Lee, H. Park, and M. S. Parihar, "The concept of electrostatic doping and related devices," *Solid. State. Electron.*, vol. 155, pp. 32–43, May 2019. [Online]. Available: https://doi.org/ 10.1016/j.sse.2019.03.017

- [16] G. Gupta, B. Rajasekharan, and R. J. E. Hueting, "Electrostatic doping in semiconductor devices," *IEEE Trans. Electron Devices*, vol. 64, no. 8, pp. 3044–3055, Aug. 2017.

- [17] C. Novo, R. Giacomini, R. Doria, A. Afzalian, and D. Flandre, "Illuminated to dark ratio improvement in lateral SOI PIN photodiodes at high temperatures," *Semicond. Sci. Technol.*, vol. 29, no. 7, 2014, Art. no. 75008. [Online]. Available: https://dx.doi.org/10.1088/0268-1242/29/7/075008

- [18] X.-Y. Cao et al., "An SOI photodetector with field-induced embedded diode showing high responsivity and tunable response spectrum by backgate," *IEEE Trans. Electron Devices*, vol. 65, no. 12, pp. 5412–5418, Dec. 2018.

- [19] J. H. T. Bakker, M. Ł. Motycki, R. J. E. Hueting, and M. S. O. Alink, "Electrical and optical characterisation of gateless 22 nm FDSOI PINdiodes at 850 nm," in *Proc. Eur. Solid-State Electron. Res. Conf.*, 2024, pp. 460–463. [Online]. Available: https://ieeexplore.ieee.org/ document/10719482/

- [20] S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices*, 3rd ed. Hoboken, NJ, USA: Wiley, 2006. [Online]. Available: http://doi.wiley. com/10.1002/0470068329

- [21] V. Puliyankot and R. J. E. Hueting, "One-dimensional physical model to predict the internal quantum efficiency of Si-based LEDs," *IEEE Trans. Electron Devices*, vol. 59, no. 1, pp. 26–34, Jan. 2012.

- [22] F. Balestra, S. Cristoloveanu, M. Benachir, J. Brini, and T. Elewa, "Double-gate silicon-on-insulator transistor with volume inversion: A new device with greatly enhanced performance," *IEEE Electron Device Lett.*, vol. 8, no. 9, pp. 410–412, Sep. 1987.

- [23] D. M. Pozar, *Microwave Engineering*, 4th ed. Hoboken, NJ, USA: Wiley, 2012.

- [24] K. H. Lee, H.-J. Park, M. Bawedin, and S. Cristoloveanu, "Carrier lifetime measurement in ultrathin FD-SOI using virtual diodes," *IEEE Trans. Electron Devices*, vol. 66, no. 4, pp. 1874–1880, Apr. 2019.

- [25] S. Radovanovic, "High-speed photodiodes in standard CMOS technology," Ph.D. dissertation, Faculty Electr. Eng. Math. Comput. Sci., Univ. Twente, Enschede, The Netherlands, 2005. [Online]. Available: https://ris.utwente.nl/ws/portalfiles/portal/6079909/ thesis\_Sasa\_Radovanovic.pdf

- [26] J. H. T. Bakker, M. S. O. Alink, J. Schmitz, and B. Nauta, "Characterisation of photodiodes in 22 nm FDSOI at 850 nm," in *Proc. Eur. Solid-State Device Res. Conf. (ESSDERC)*, 2023, pp. 65–68.